Name:

**Enrolment No:**

# UNIVERSITY OF PETROLEUM AND ENERGY STUDIES

# **End Semester Examination, December 2022**

**Programme Name: B. Tech (Electronics & Communication Engineering)**

Semester : VII : 3:00 hrs **Course Name** : VLSI Design Time

Course Code : ECEG-4001 Max. Marks: 100

Nos. of page(s) : 02

Instructions: Assume any data in programming, if required.

#### **SECTION A (4 x 5 = 20 Marks)**

# Attempt all the questions

**Q.1** Explain the concept of body effect in MOSFET.

[4 M] [CO1]

**Q.2** List the different parameters of the MOSFET and drive relation between them.

[4 M] [CO1]

**Q.3** Write the all steps in the FPGA Design flow.

[4 M] [CO5]

**Q.4** What is the need of low power CMOS circuit design? Draw the voltage transfer characteristics of CMOS.

[4 M] [CO4]

**Q.5** Detail the logic simulation of synchronous positive edge 'T' Flip-flop using VHDL.

[4 M] [CO5]

## Section-B $(4 \times 10 = 40 \text{ Marks})$

## Attempt *all* the questions

Q.6 Detail the functionality of enhancement type NMOS under different regions. Derive the mathematical equations of the drain current for NMOS in all the regions. [10 M] [CO1]

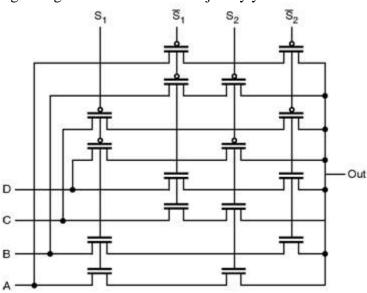

Q.7 (a) Realize the following functions using NMOS and CMOS.

[6 M] [CO3]

$$Y = \overline{A.(B + CD)}$$

(b) Write the output of the logic diagram shown below and justify your answer.

[4 M] [CO4]

Fig.1 CMOS Logic

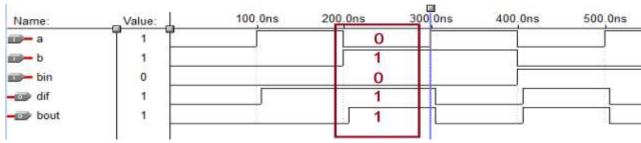

**Q.9** (a) Draw the logic diagram to support the following timing waveform and develop the code in VHDL to support the functionality. [10 M] [CO5]

Fig.2 Waveform

#### OR

(b) What are the different styles of modeling in VHDL? Design (3 x 8) decoder using any two styles of modeling, logic diagram and timing simulation waveform. [10 M] [CO5]

### Section-C $(2 \times 20 = 40 \text{ Marks})$

Attempt any two of the followings

Q.10 (a) Draw the voltage transfer curve for the NMOS inverter and derive the mathematical expression to estimate the value of V<sub>OH</sub>, and V<sub>IL</sub> for NMOS inverter circuit and detail the functionality. [10 M] [CO3] (b) Draw the CMOS logic layout and stick diagram of inverter, 2 input XOR and NOR gates. [10 M] [CO3]

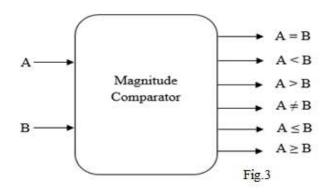

- Q.11 The purpose of a digital comparator is to compare a set of variables or unknown numbers, for example A (A1, A2, A3... An, etc) against that of a constant or unknown value such as B (B1, B2, B3,... Bn, etc) and produce an output condition or flag depending upon the result of the comparison. For example, a magnitude comparator of two 1-bits, (A and B) inputs would produce the following three output conditions when compared to each other. This is useful if we want to compare two variables and want to produce an output when any of the above three conditions are achieved. For example, produce an output from a counter when a certain count number is reached. Consider the case of 64-bit comparator for the different logic functions.

- (a) Develop the VHDL/ Verilog HDL code to support the functionality of design

- (b) Estimate the different test cases and test benches of the design.

- (c) Design an ALU chip that accepts 32-bit data and perform at least 10 operations using VHDL. [20] [CO4]

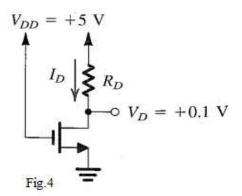

Q.12 (a) Draw and explain the small signal models of PMOS, NMOS and BiCMOS. [10M] [CO2](b) Design the circuit shown in Fig.4 to establish a drain voltage of 0.1 V. What is the effective resistance

between drain and source at this operating point Let Vt = 1V, and  $K'n(W/L) = 1mA/V^2$ . [10M] [CO2]