Name:

**Enrolment No:**

## UNIVERSITY OF PETROLEUM AND ENERGY STUDIES End Semester Examination, June 2021

Course: Computer System Architecture

Program: B.Tech-CSE

Course Code: CSEG1014

Semester: II

Time : 03 hrs.

Max. Marks: 100

| Instruction: Attempt all questions. Internal choice is given, where ever applicable. |                                                                                                                                                                                                                                                                                                             |                  |     |  |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|--|--|--|--|

| SECTION A                                                                            |                                                                                                                                                                                                                                                                                                             |                  |     |  |  |  |  |

| 1. Each Question will carry 5 Marks                                                  |                                                                                                                                                                                                                                                                                                             |                  |     |  |  |  |  |

| S. No.                                                                               |                                                                                                                                                                                                                                                                                                             | Marks            | CO  |  |  |  |  |

| Q 1                                                                                  | Reduce the following using Boolean Algebra (Type A' in place of $\overline{A}$ wherever applicable.)  (i) $Z = A \left[ B + C(AB + AC) \right]$ (ii) $Z = \overline{ABC} + (\overline{A+B+C}) + \overline{ABCD}$ .                                                                                          | 2.5 +<br>2.5 = 5 | CO2 |  |  |  |  |

| Q 2                                                                                  | Convert the following as indicated by their base: (Type only the final answer).  (i) $(650)_{10} \rightarrow ( )_{16}$ (ii) $(CA57)_{16} \rightarrow ( )_{2}$ (iii) $(7BF)_{16} \rightarrow ( )_{2}$ (iv) $(110101)_{2} \rightarrow ( )_{8}$ (v) $(E7F6)_{16} \rightarrow ( )_{10}$                         | 1 X 5<br>= 5     | CO2 |  |  |  |  |

| Q 3                                                                                  | Name the addressing modes involved in the following operations:  (i) Pointer  (ii) Program Relocation  (iii) Array Operation  (iv) Stack Operation  (v) Constant assignment.                                                                                                                                | 1 X 5<br>= 5     | CO3 |  |  |  |  |

| Q 4                                                                                  | Differentiate  (i) Hardwired control unit vs. Microprogrammed control unit.  (ii) CISC vs. RISC                                                                                                                                                                                                             | 2.5 + 2.5 = 5    | CO3 |  |  |  |  |

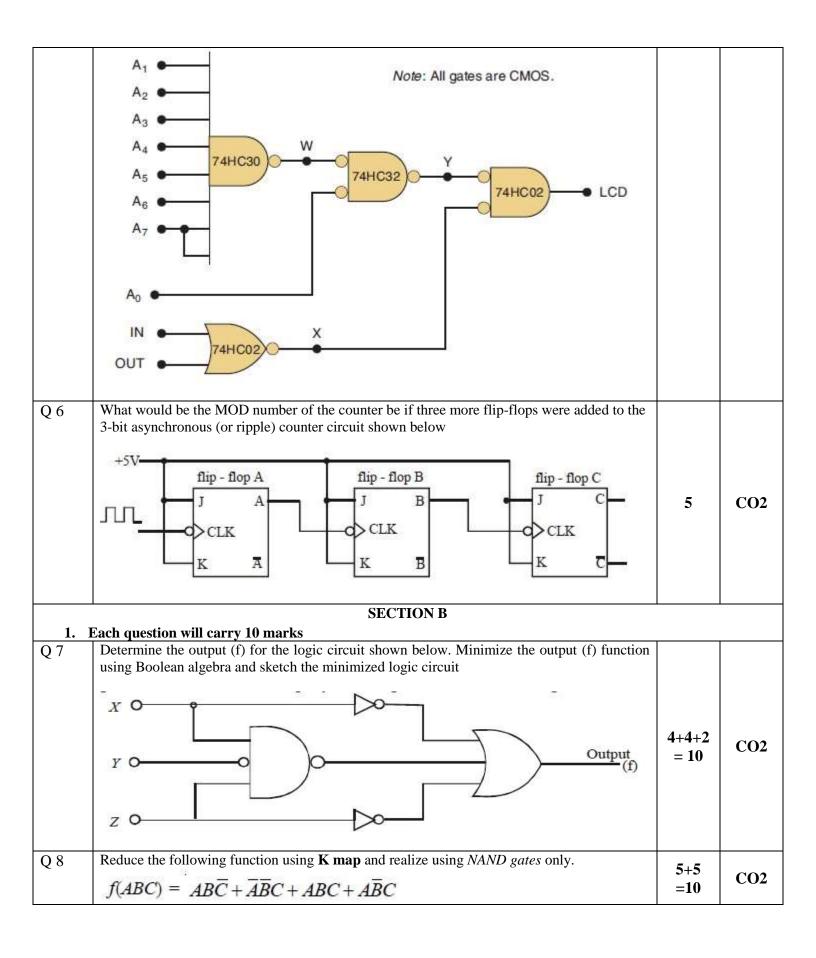

| Q 5                                                                                  | The logic circuit shown below enables the liquid crystal display (LCD) of a handheld electronic device when the microcontroller is sending data to or receiving data from the LCD controller. The circuit will enable the display when LCD = 1. Determine the input conditions necessary to enable the LCD. | 5                | CO1 |  |  |  |  |

| 0.0      | (:)           | Evaluin about paints board interpret contain                                                               |               |                 |

|----------|---------------|------------------------------------------------------------------------------------------------------------|---------------|-----------------|

| Q 9      | (i)           | Explain about priority based interrupt system.  Differentiate between vectored and non-vectored interrupt. | 3+2+2         |                 |

|          | (ii)<br>(iii) | What is the main disadvantage of polling?                                                                  | +3 =10        | CO4             |

|          | (iv)          | Briefly explain about DMA?                                                                                 | +3 =10        |                 |

| Q 10     | (i)           | What is content addressable memory?                                                                        |               |                 |

| Q IO     | (ii)          | A digital computer has a memory unit of (64K X 16) and a cache memory                                      |               |                 |

|          | (11)          | of 1K words. The cache uses direct mapping with a block size of 4 words.                                   |               |                 |

|          |               | (a) How many bits are there in the tag, index, block, and word fields of the                               | 2+3+3         |                 |

|          |               | address format?                                                                                            | +2 = 10       | CO4             |

|          |               | (b) How many bits are there in each word of cache, and how are they                                        | 10            |                 |

|          |               | divided into functions? Include a valid bit.                                                               |               |                 |

|          |               | (c) How many blocks can the cache accommodate?                                                             |               |                 |

| Q 11     | Explain t     | he following                                                                                               |               |                 |

| Q 11     | (i)           | Instruction Cycle                                                                                          |               |                 |

|          | (ii)          | Fetch Cycle                                                                                                | 2 X 5         |                 |

|          | (iii)         | Execution Cycle                                                                                            | = 10          | CO1             |

|          | (iv)          | Instruction Format                                                                                         |               |                 |

|          | (v)           | Types of Instructions                                                                                      |               |                 |

|          |               | SECTION-C                                                                                                  |               |                 |

|          |               | Each Question carries 20 Marks.                                                                            |               |                 |

| Q 12     | (i) E         | xplain in detail about the various addressing modes.                                                       |               |                 |

|          | (ii) W        | Trite a sequence of assembly level instructions that will compute the value                                |               |                 |

|          | of            | $f\{\mathbf{x} = (\mathbf{A} + \mathbf{B}) * (\mathbf{C} + \mathbf{D})\} \text{ using}$                    | <b>10+ 10</b> | CO3             |

|          | (a            | Three-address instructions                                                                                 | = 20          | COS             |

|          | (b            |                                                                                                            |               |                 |

|          | (0            | c) One-address instructions                                                                                |               |                 |

|          |               | OR                                                                                                         |               |                 |

|          | ` ′           | /rite short notes on                                                                                       |               |                 |

|          | (a            | n) Memory Address Register (MAR)                                                                           |               |                 |

|          |               | b) Memory Data Register (MDR)                                                                              |               |                 |

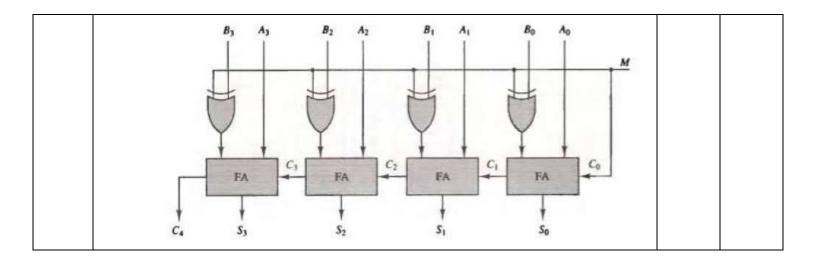

|          |               | he adder-subtractor circuit shown below has the following values for input                                 |               |                 |

|          |               | node M and data inputs A and B. In each case, determine the values of the                                  |               |                 |

|          | 01            | utputs: S3, S2, S1, S0, and C4                                                                             |               |                 |

|          | _             |                                                                                                            | 5 +5 +        |                 |

|          |               | M A B                                                                                                      | 10 = 20       | CO <sub>3</sub> |

|          | <u> </u>      | a 0 0111 0110                                                                                              | 10 –20        |                 |

|          |               | b 0 1000 1001                                                                                              |               |                 |

|          |               | c 1 1100 1000                                                                                              |               |                 |

|          |               | d 1 0101 1010                                                                                              |               |                 |

|          |               | e 1 0000 0001                                                                                              |               |                 |

|          |               | РТО                                                                                                        |               |                 |

| <u> </u> |               | 110                                                                                                        |               |                 |