**Enrolment No:**

## UNIVERSITY OF PETROLEUM AND ENERGY STUDIES End Semester Examination, July 2020

Course: DIGITAL ELECTRONICS Program: B.Tech Electrical Engineering Course Code: ECEG 2016 Semester: IV Time 03 hrs. Max. Marks: 100

**Instructions:**

- 1. Attempt all the questions (Theory, Numerical, Case study etc.) on A4 size blank sheets.

- 2. Attempt all questions serially as per question paper.

- **3.** Answer should be neat and clean. Draw a free hand sketch for circuits/tables/schematics wherever required.

- 4. Scan the whole answer script and check the resolution carefully before upload on the blackboard. Note that answer scripts will be considered for evaluation only through Blackboard. No other mode of submission is acceptable.

- 5. You are expected to be honest about each attempt which you make to progress in life

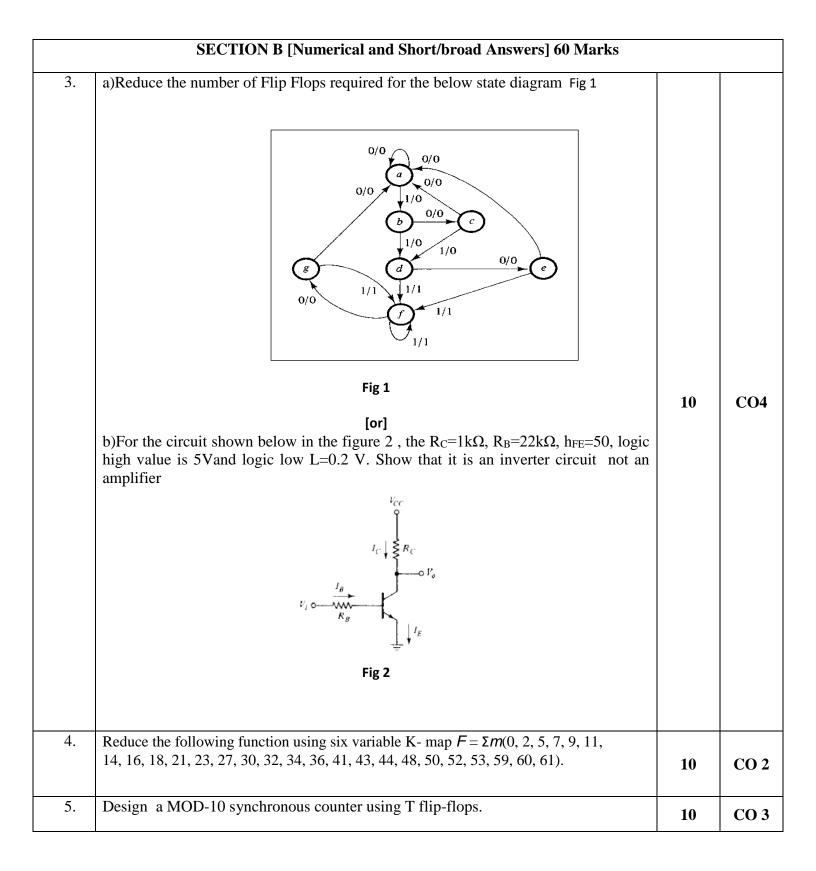

| S. No. |                                                                                                                                                                                                                                                                                                                                         | Marks | CO                |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|

| 1.     | Design a Seven segment display decoder for the<br>(i) numbers 0-9<br>(ii) for 10 as 'A'<br>(iii) for 11 as 'B'<br>(iv) for 12 as 'C'<br>(v) for 13 as 'D'<br>(vi) for 14 as 'E'<br>(vii) for 15 as 'F'                                                                                                                                  | 20    | COS               |

| 2.     | a)Implement the following Boolean functions using PAL with four inputs with<br>AND- OR structure. $F_1(A,B,C,D)=\Sigma m(2,12,13)$<br>$F_2(A,B,C,D)=\Sigma m(7-15)$<br>$F_3(A,B,C,D)=\Sigma m(0,2-8,10,11,15)$<br>$F_4(A,B,C,D)=\Sigma m(1,2,8,12,13)$<br>b)Design a PLA circuit to implement the 3-bit binary to Gray code conversion. | 15+5  | CO a<br>&<br>CO a |

NOTE : The submission time of the Question Paper Answer Sheet is 24 Hhrs from the scheduled time (exceptional provision due to extraordinary circumstance due to COVID-19 and due to internet connectivity issues in the farflung areas).

No Submission will be entertained after 24 Hrs

NOTE : The submission time of the Question Paper Answer Sheet is 24 Hhrs from the scheduled time (exceptional provision due to extraordinary circumstance due to COVID-19 and due to internet connectivity issues in the farflung areas).

No Submission will be entertained after 24 Hrs

| 6. | Explain about the         (i)Edge triggering       (ii) Master Slave Flip Flop         (iii)Race Around       (iv) Indeterminate state (v)Noise Margin in Logic circuits                                                                                                                                                           | 5       | CO1  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| 7. | Design a multiplexer circuit which implements the function $F_1(A,B,C,D,E)=\Sigma m(0, 2, 5, 7, 9, 11, 12, 13, 17, 19, 22, 28, 29,)$                                                                                                                                                                                               | 10      | CO2  |

| 8. | <ul> <li>(i)Design of R-2R ladder D/A Converter for four bit binary number conversion into analog equivalent</li> <li>(ii)A 4 bit R-2R ladder type D/A Converter having resistor values of R=10kΩ and 2R=20kΩ uses V<sub>R</sub> of 10 V. Find (i)the resolution of the D/A Converter, (ii)for a digital input of 1011.</li> </ul> | 5<br>10 | CO 4 |

NOTE : The submission time of the Question Paper Answer Sheet is 24 Hhrs from the scheduled time (exceptional provision due to extraordinary circumstance due to COVID-19 and due to internet connectivity issues in the far-flung areas).

No Submission will be entertained after 24 Hrs