# MULTI-STATE LOGIC FOR COMPUTATION

A thesis submitted to the University of Petroleum and Energy Studies

> For the Award of **Doctor of Philosophy** in Computer Science & Engineering

> > BY Amit Verma

Novomber 2019

SUPERVISOR Dr. Manish Prateek

School Of Computer Science University Of Petroleum & Energy Studies Dehradun-248007: Uttarakhand

# MULTI-STATE LOGIC FOR COMPUTATION

A thesis submitted to the University of Petroleum and Energy Studies

> For the Award of **Doctor of Philosophy** in Computer Science & Engineering

> > BY Amit Verma (SAP ID 500048922)

> > > Novomber 2019

SUPERVISOR Dr. Manish Prateek Professor & Dean School Of Computer Science University Of Petroleum & Energy Studies

School Of Computer Science University Of Petroleum & Energy Studies Dehradun-248007: Uttarakhand

# November 2019 DECLARATION

I declare that the thesis entitled MULTI-STATE LOGIC FOR COMPUTA-TION has been prepared by me under the guidance of DR. MANISH PRATEEK, Professor & Dean of School Of Computer Science, University Of Petroleum & Energy Studies. No part of this thesis has formed the basis for the award of any degree or fellowship previously.

Amit Verma

School Of Computer Science University Of Petroleum & Energy Studies P.O. Bidholi Via-Prem Nagar, Dehradun-248007 DATE :

### CERTIFICATE

I certify that Amit Verma has prepared his thesis entitled MULTI-STATE LOGIC FOR COMPUTATION, for the award of PhD degree of the University of Petroleum & Energy Studies, under my guidance. He has carried out the work at the Department of Informatics, University of Petroleum & Energy Studies.

Dr. Manish Prateek Professor & Dean of School Of Computer Science University Of Petroleum & Energy Studies P.O. Bidholi Via-Prem Nagar, Dehradun-248007 DATE :

IV

CORPORATE OFFICE: 210. 2<sup>-4</sup> Floor. Okhla Industrial Estate, Phase III. New Delhi - 110 020. Incla. 1. +91 1. 41750151/55, 46022691/5 5: +91 11.41750154 ENERGY ACRES: Bidholi Via Prem Nagar, Dehradun - 248 007 (Uttarakhand), India. T: +91 135 2770137, 2776053/54/91, 2776201 F: +91 135 2776090/95 KNOWLEDCE ACRES: Kandoli Via Prem Nagar, Dehradun - 248 007 (Uttarakhand), India T: +91 8171979021/2/3, 7060111775

INGINEERING | COMPUTER SCIENCE | DESIGN | BUSINESS | LAW | HEALTH SCIENC

#### ABSTRACT

In this thesis, work is divided in mainly two parts contributing in the field of multiplication operation and multivalued logic.

Multiplication is one of the important arithmetic operation both in manual mathematics and digital machine, methods of multiplication travels from the time of Vedas till today. Many methods of performing multiplication are mention in Vedic literature but most of the researcher mainly used *urdhva tiryakbhya* and *nikhilam* sutra for designing binary multiplexer which are more complex and require large number of electronic components with interconnection overhead results in delay. Moreover, previously developed Vedic multiplexers for binary machine are totally based on Vedic sutra, no modification has been done or no novel approach is derived from the Vedic literature. In this work, a novel algorithm is proposed for the multiplication of binary numbers motivated from various untouched methods mention in the Vedic literature. The algorithm mainly consist of one main algorithm that is am-Multiplication and two sub-algorithms MIN & MAX, a binary multiplexer circuit is also design on the basis of the proposed algorithm for performing binary multiplication.

Multivalued logic simply means increasing the logical states of machine on the basis of the level of voltages, which can be consider as an alternate for the traditional binary system to improve the computation speed & storage efficiency. Furthermore for reducing the number of electronic components, interconnection overhead, delay and chip size. Here, a novel algorithm is proposed for performing ternary addition where ternary system comprises of three logical states (bits)  $\{0, 1, \& 2\}$  instead of two logical states  $\{0 \& 1\}$  as in case of traditional binary system. Stack of size 1 is used in the algorithm for holding generated carry bit, where in case of ternary addition

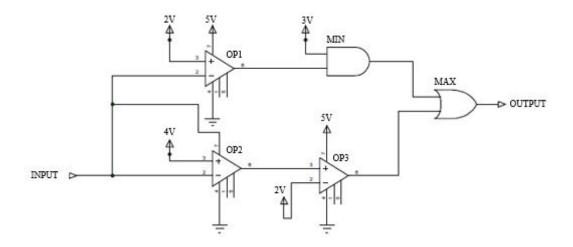

carry is only generated when both the bits are non-zero and either of the bit is 2. Truth table for various ternary operators are proposed, based on which the circuits are design using op-amp 741 IC, 7432 IC & 7208 IC. Single ternary inverter(t-NOT) circuit is proposed which can be consider as an extension of binary NOT gate replacing the previously developed three separate circuits for ternary inverter. The circuit for ternary decoder, ternary NAND & NOR gate also proposed in the work. The t-NOT gate is considered as building block for designing circuits based on ternary logic. And on the basis of these ternary operators an adder circuit is designed which comprises of separate circuit for computing sum and generated carry. The proposed ternary adder circuit is based on the truth table representing the sum and carry for all possible combinations of two ternary bits either of which can be from the set of three logical bits  $\{0, 1, \& 2\}$ .

keywords : Vedic literature, multiplication, multivalued Logic, ternary inverter.

#### ACKNOWLEDGEMENT

I bow my head humbly to pay heart felt regards to Almighty God for giving me the strengths and blessing in completing this thesis.

There are quite a few people that have helped me in one way or another to the completion of this work. It is with great pleasure, I would like to thank all of you from very deep inside.

Foremost, I would like to express my sincere gratitude to my thesis advisor Prof. Manish Prateek, for picking me up as a student at the critical stage of my career and the continuous support of my Ph.D study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis.

It is absolutely difficult to succeed in the process of finding and developing an idea without the help of a specialist in the domain. I found in my advisor not only the source of wonderful ideas to develop, but also the support that a Ph.D student needs. I could not have imagined having a better advisor and mentor for my Ph.D study.

Besides my advisor, I would like to thank Chancellor Dr. S. J. Chopra, Vice chancellor Dr. Deependra Kumar Jha, Dean Dr. Kamal Bansal at the University of Petroleum and Energy Studies for their encouragement, suggestions and valuable support for my research work.

I would like to express my special thanks to Dr. J K Pandey, R&D, Director and Dr. Rakhi Ruhal, Program Manager-Ph.D, University of Petroleum and Energy Studies, for his assistance during my research work. I am grateful to the University of Petroleum and Energy Studies, for giving me an opportunity to pursue my research and for providing all facilities in the Department of Studies in School of Computer Science and Engineering.

I would like to thank all the Heads of School of Computer Science Departments, doctoral students for their feedback, cooperation, and of course friendship. In addition I would like to express my gratitude to all colleagues in the university. In particular, I am grateful to Dr. Pradeep Kumar for his patiance, support and being with me in all my hard times.

Last but not the least, I would like to thank my family especially to my mother Smt. Raj Rani Verma for supporting me spiritually throughout writing this thesis and my life in general.

# TABLE OF CONTENTS

| List of | ' Table | s                                                                                                  | xii |

|---------|---------|----------------------------------------------------------------------------------------------------|-----|

| List of | Figur   | $\operatorname{es}$                                                                                | XV  |

| Chapt   | er 1: I | ntroduction                                                                                        | 1   |

| 1.1     | Multij  | plication Operation                                                                                | 1   |

|         | 1.1.1   | Kapata – sandhi                                                                                    | 5   |

|         | 1.1.2   | Gelosia method                                                                                     | 5   |

|         | 1.1.3   | Vajrabhyasa method                                                                                 | 6   |

|         | 1.1.4   | Sthana – Khanda                                                                                    | 7   |

|         | 1.1.5   | Gomutrika method                                                                                   | 8   |

|         | 1.1.6   | Ista – Ganana method                                                                               | 8   |

| 1.2     | Terna   | ry(3-state) Logic $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 10  |

| 1.3     | Motiv   | ation $\ldots$    | 13  |

|         | 1.3.1   | Multiplication Algorithm                                                                           | 13  |

|         | 1.3.2   | Ternary operators & Adder                                                                          | 13  |

| Chapt   | er 2: I | Literature Review                                                                                  | 15  |

| 2.1     | Multij  | plication Operation                                                                                | 15  |

| 2.2     | Multi   | valued Logic                                                                                       | 22  |

| Chapte | er 3: AM-Multiplication Algorithm & Based Multiplexer                        | 32          |  |  |  |  |

|--------|------------------------------------------------------------------------------|-------------|--|--|--|--|

| 3.1    | AM-Multiplication Algorithm                                                  | 32          |  |  |  |  |

|        | 3.1.1 Development of Sets and Equations                                      | 33          |  |  |  |  |

|        | 3.1.2 am-MULITPLICATION Algorithm                                            | 38          |  |  |  |  |

|        | 3.1.3 Circuit Diagram for Binary Multiplexer based on am-MULTIPLIC Algorithm | ATION<br>42 |  |  |  |  |

| Chapte | er 4: Multistate Logic (3-state)                                             | 45          |  |  |  |  |

| 4.1    | t-NOT gate (inverter circuit)                                                | 47          |  |  |  |  |

|        | 4.1.1 Circuit diagram of t-NOT gate                                          | 51          |  |  |  |  |

| 4.2    | p-NAND & s-NAND gate                                                         | 54          |  |  |  |  |

| 4.3    | p-NOR & s-NOR gate                                                           | 56          |  |  |  |  |

| 4.4    | Ternary Decoder                                                              |             |  |  |  |  |

| 4.5    | Ternary Addition Algorithm                                                   | 60          |  |  |  |  |

| 4.6    | Ternary Adder                                                                | 64          |  |  |  |  |

| Chapte | er 5: Results and Discussion                                                 | 68          |  |  |  |  |

| 5.1    | am-MULTIPLICATION Algorithm                                                  | 68          |  |  |  |  |

| 5.2    | Ternary inverter circuit                                                     | 72          |  |  |  |  |

| 5.3    | p-NAND & s-NAND gate                                                         | 74          |  |  |  |  |

| 5.4    | p-NOR & s-NOR gate                                                           | 77          |  |  |  |  |

| 5.5    | Ternary Decoder                                                              | 80          |  |  |  |  |

| 5.6    | Ternary Adder                                                                | 82          |  |  |  |  |

| 5.7    | Ternary Addition Algorithm and MIN & MAX gate Logic                          | 89          |  |  |  |  |

| Chapter 6:  | Conclusion and Future Scope | 92 |

|-------------|-----------------------------|----|

| References  |                             | )1 |

| Publication | ns                          | )2 |

# LIST OF TABLES

| 1.1  | Pingala chandah-sutra                                                                              | 4  |

|------|----------------------------------------------------------------------------------------------------|----|

| 1.2  | Voltage representation of the logical states of ternary logic, where $v$ is voltage                | 13 |

| 2.1  | Summary of Related Work                                                                            | 22 |

| 2.2  | Summary of Related Work                                                                            | 31 |

| 4.1  | Truth Table of binary NOT Gate                                                                     | 46 |

| 4.2  | Truth Table of Ternary Inverter Gate                                                               | 47 |

| 4.3  | Truth Table t-NOT Gate                                                                             | 49 |

| 4.4  | Working of 741 op-amp                                                                              | 51 |

| 4.5  | Working of 741 op-amp when VIN is greater than +VCC                                                | 52 |

| 4.6  | Reading of 741 op-amp when VIN is greater than +VCC $\ldots$ .                                     | 52 |

| 4.7  | Reading of 7432 IC & 7408 IC returning maximum and minimum volt-<br>age among the supplied inputs. | 53 |

| 4.8  | Truth Table for Ternary p-NAND and s-NAND gate                                                     | 54 |

| 4.9  | Truth Table for Ternary p-NOR and s-NOR gate                                                       | 57 |

| 4.10 | Truth table for 2:4 binary decoder                                                                 | 59 |

| 4.11 | Truth table for ternary decoder                                                                    | 59 |

| 4.12 | Truth Table for performing Ternary Addition                                                        | 61 |

| 4.13 | 3-bit Ternary equivalent of first eighteen natural numbers of base $10$ .                                       | 62 |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| 4.14 | Time complexity of the proposed algorithm                                                                       | 64 |  |  |  |  |

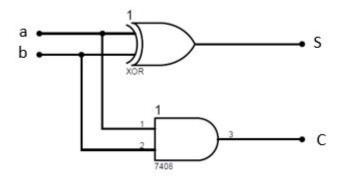

| 4.15 | 6 Binary Half Adder                                                                                             |    |  |  |  |  |

| 4.16 | Truth Table for Ternary Adder                                                                                   | 66 |  |  |  |  |

| 5.1  | Gate count and gate delay for three types of $8x8$ multiplexers                                                 | 71 |  |  |  |  |

| 5.2  | Calculated delays in ns based on VHDL Synthesis report for 8x8 mul-<br>tiplexers                                | 71 |  |  |  |  |

| 5.3  | Calculated delays in ns based on VHDL Synthesis report for 16x16 multiplexers                                   | 72 |  |  |  |  |

| 5.4  | Voltage at each component in circuit of t-NOT Gate                                                              | 74 |  |  |  |  |

| 5.5  | Truth Table t-NOT Gate                                                                                          | 74 |  |  |  |  |

| 5.6  | Voltage distribution in the circuit of p-NAND gate                                                              | 76 |  |  |  |  |

| 5.7  | Voltage distribution in the circuit of s-NAND gate                                                              | 77 |  |  |  |  |

| 5.8  | Voltage distribution in the circuit of p-NOR gate                                                               | 79 |  |  |  |  |

| 5.9  | Voltage distribution in the circuit of s-NOR gate                                                               | 80 |  |  |  |  |

| 5.10 | Truth Table Ternary Decoder                                                                                     | 81 |  |  |  |  |

| 5.11 | Ternary Decoder                                                                                                 | 82 |  |  |  |  |

| 5.12 | Voltage across the circuit when the output line $X_0$ of ternary decoder<br>is enabled (E)                      | 83 |  |  |  |  |

| 5.13 | Voltage across the circuit when the output line $X_1$ of ternary decoder<br>is enabled (E)                      | 84 |  |  |  |  |

| 5.14 | Voltage across the circuit when the output line $X_2$ of ternary decoder<br>is enabled (E)                      | 85 |  |  |  |  |

| 5.15 | Voltage across the circuit for calculating carry C when the output line $X_1$ of ternary decoder is enabled (E) | 87 |  |  |  |  |

| 5.16 | Voltage act | ross t | the | circuit | when | the | output | line | $X_2$ of | ternary | decoder |    |

|------|-------------|--------|-----|---------|------|-----|--------|------|----------|---------|---------|----|

|      | is enabled  | (E)    |     |         |      |     |        |      |          |         |         | 89 |

# LIST OF FIGURES

| 1.1 | Sloke mention in Vedanga Jyotisa                                                                                                                                                              | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Sloke for Sthanangasutra                                                                                                                                                                      | 2  |

| 1.3 | Sloke for Pingala Sutra                                                                                                                                                                       | 3  |

| 1.4 | Kapata - sandhi method                                                                                                                                                                        | 5  |

| 1.5 | Gelosia method                                                                                                                                                                                | 6  |

| 1.6 | Vajrabhyasa method                                                                                                                                                                            | 7  |

| 1.7 | Sthana - Khanda method                                                                                                                                                                        | 7  |

| 1.8 | Gonutrika method                                                                                                                                                                              | 8  |

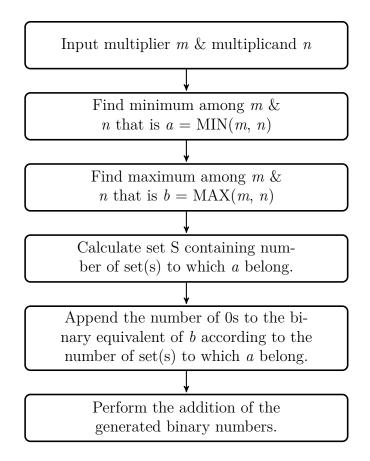

| 3.1 | Work Flow representing the basic steps involved the proposed am-<br>Multiplication algorithm.                                                                                                 | 33 |

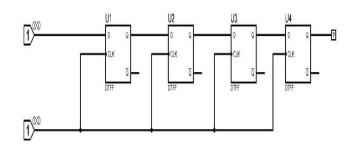

| 3.2 | Shift Register to shift the binary number bit by bit                                                                                                                                          | 43 |

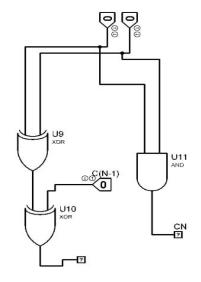

| 3.3 | Carry Look-ahead Full Adder for the summation of generated carry<br>and the input received form shift registers                                                                               | 43 |

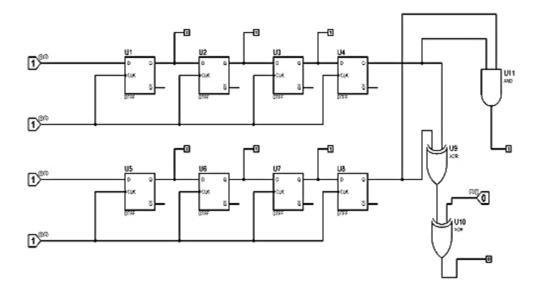

| 3.4 | Circuit based on am-MULTIPLICATION algorithm in which the output of the shift registers and the generated carry of previous state act as input to carry look-ahead adder for binary addition. | 44 |

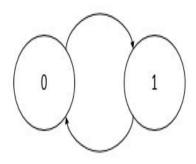

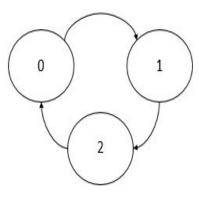

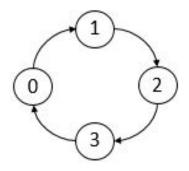

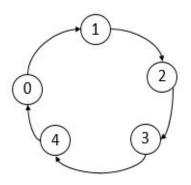

| 4.1 | State Transition Diagram for Binary NOT gate                                                                                                                                                  | 49 |

| 4.2 | State Transition Diagram for Ternary NOT gate                                                                                                                                                 | 49 |

| 4.3 | State Transition Diagram for NOT gate for 4-state machine                                                                                                                                     | 49 |

| 4.4  | State Transition Diagram for NOT gate for 5-state machine                                                                                                                                                                                                                                                                                                          | 50 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5  | Proposed symbol for Ternary NOT gate                                                                                                                                                                                                                                                                                                                               | 51 |

| 4.6  | Circuit for t-NOT gate                                                                                                                                                                                                                                                                                                                                             | 52 |

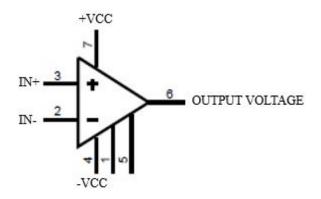

| 4.7  | Circuit for 741 op-amp                                                                                                                                                                                                                                                                                                                                             | 52 |

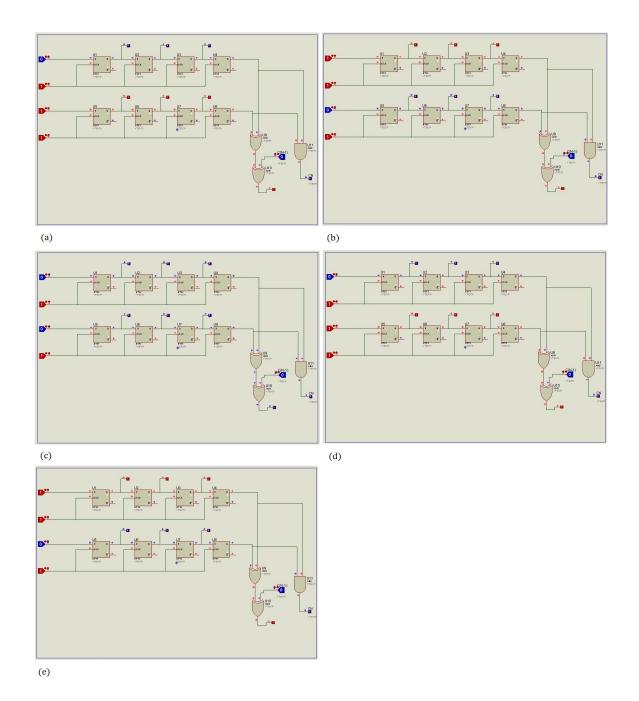

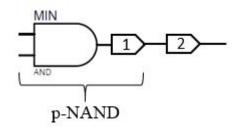

| 4.8  | Symbolic diagram for p-NAND gate                                                                                                                                                                                                                                                                                                                                   | 55 |

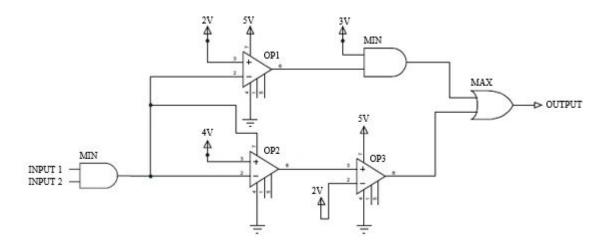

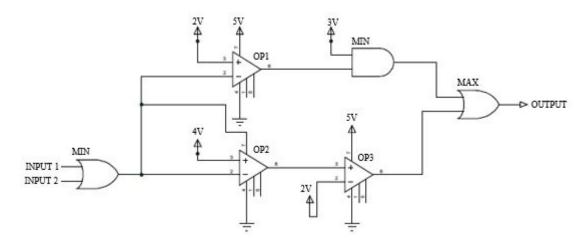

| 4.9  | Symbolic diagram for s-NAND gate                                                                                                                                                                                                                                                                                                                                   | 55 |

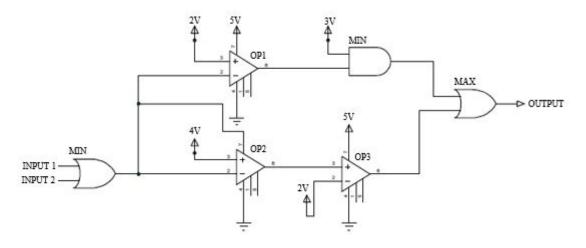

| 4.10 | Circuit diagram for p-NAND gate                                                                                                                                                                                                                                                                                                                                    | 55 |

| 4.11 | Circuit diagram for s-NAND gate                                                                                                                                                                                                                                                                                                                                    | 56 |

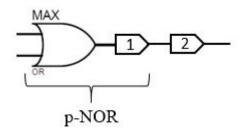

| 4.12 | Symbolic diagram for p-NOR gate                                                                                                                                                                                                                                                                                                                                    | 57 |

| 4.13 | Symbolic diagram for s-NOR gate                                                                                                                                                                                                                                                                                                                                    | 57 |

| 4.14 | Circuit diagram for p-NOR gate                                                                                                                                                                                                                                                                                                                                     | 58 |

| 4.15 | Circuit diagram for s-NOR gate                                                                                                                                                                                                                                                                                                                                     | 58 |

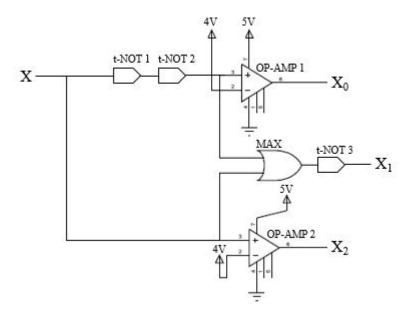

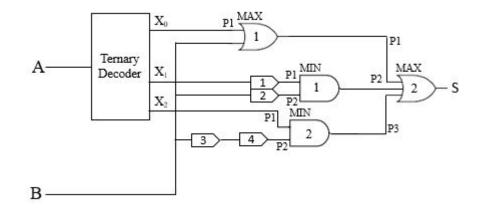

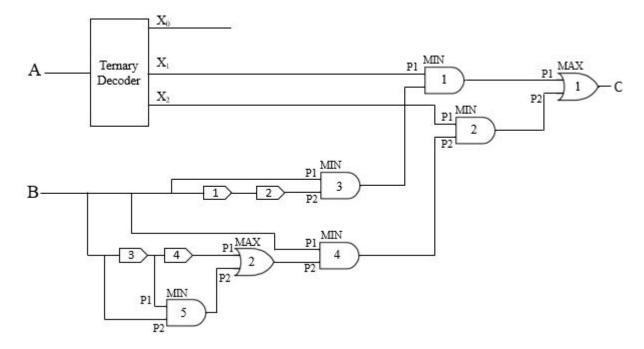

| 4.16 | Circuit diagram for Ternary Decoder                                                                                                                                                                                                                                                                                                                                | 60 |

| 4.17 | Circuit diagram for Binary Half Adder                                                                                                                                                                                                                                                                                                                              | 65 |

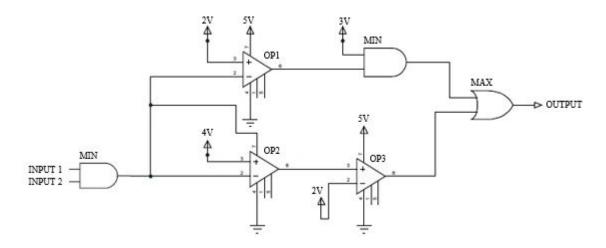

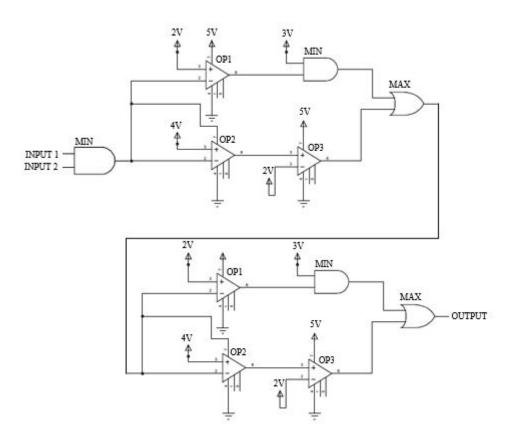

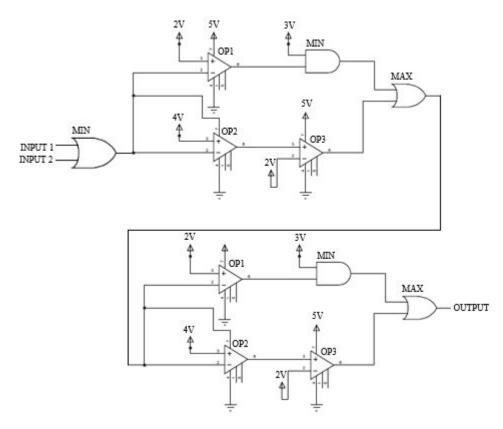

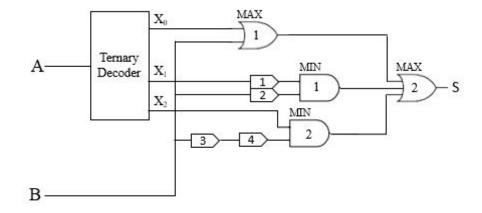

| 4.18 | Circuit diagram for Ternary Adder for computation of sum S $\ldots$ .                                                                                                                                                                                                                                                                                              | 66 |

| 4.19 | Circuit diagram for Ternary Adder for computation of carry C $\ . \ . \ .$                                                                                                                                                                                                                                                                                         | 67 |

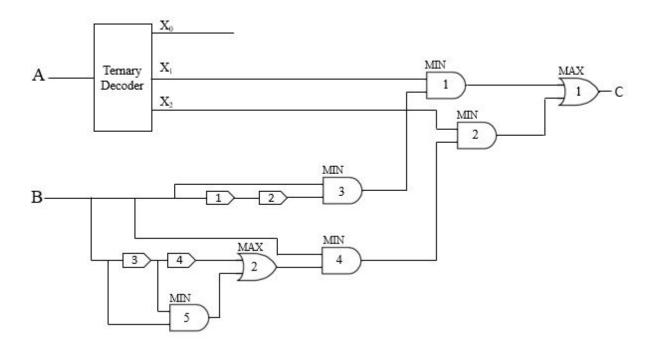

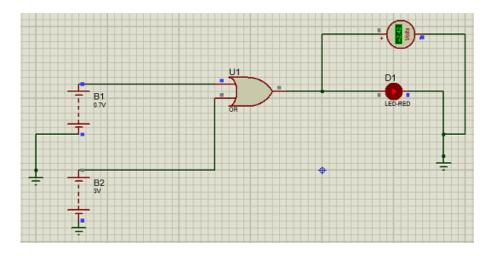

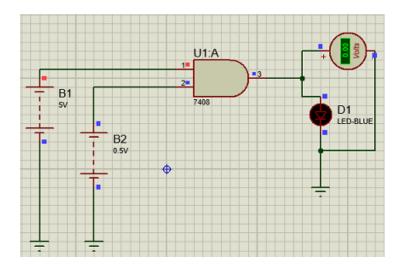

| 5.1  | Results on Proteus 8 (a) The output of carry look-ahead adder Sum = 1 for $y = 0$ , $x = 1$ generated from shift registers and carry $C(N-1) = 0$ (b) Now, Sum = 1 for $y = 1$ , $x = 0$ and $C(N-1) = 0$ (c) Sum = 0 for $y = 0$ , $x = 0$ and $C(N-1) = 0$ (d) Sum = 1 for $y = 0$ , $x = 1$ and $C(N-1) = 0$ (e) Sum = 1 for $y = 1$ , $x = 0$ and $C(N-1) = 0$ | 70 |

| 5.2  | Symbolic diagram for s-NAND gate                                                                                                                                                                                                                                                                                                                                   | 75 |

| 5.3  | Circuit diagram for p-NAND gate                                                                                                                                                                                                                                                                                                                                    | 75 |

| 5.4  | Circuit diagram for p-NOR gate                                                                                                                                                                                                                                                                                                                                     | 78 |

| 5.5 | Symbolic diagram for s-NOR gate                                                      | 80  |

|-----|--------------------------------------------------------------------------------------|-----|

| 5.6 | Circuit of ternary adder for calculating sum S $\ \ldots \ \ldots \ \ldots \ \ldots$ | 83  |

| 5.7 | Circuit of ternary adder for calculating calculating carry C $\ . \ . \ .$ .         | 86  |

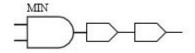

| 5.8 | Binary OR gate return maximum among the applied inputs voltages .                    | 90  |

| 5.9 | Binary AND gate return minimum among the applied inputs voltages                     | 90  |

| 6.1 | Circuit for a Ternary Decoder                                                        | 102 |

| 6.2 | Circuit for a Ternary NAND and NOR gate                                              | 103 |

# CHAPTER 1 INTRODUCTION

This section is divided into two major parts one is about the multiplication operation and another is ternary logic. In the section of multiplication operation, early sources of multiplication, various Vedic methods of multiplication are discussed with the introduction about the proposed work which includes the development of novel multiplication algorithm inspired by various Vedic multiplication methods. The proposed multiplication algorithm is extended for the multiplication of binary numerals. And the corresponding multiplexer circuit is also developed based on the proposed algorithm. In the section of ternary logic, basic information about multi-state logic is discussed with the proposed circuitry and functionality of various operators, decoder, and adder based on ternary logic. This is also discussed how the proposed work can be a better approach as compared to the already existing approaches.

### 1.1 Multiplication Operation

Multiplication is one of the basic and very important arithmetic operations from the Vedic period. We have tried to find out the starting point of the evolution of mathematics for that various Vedic literature is considered which are having traces of mathematics. According to various commentaries and the translation is done for Vedas, Vedanga Jyotisa [1, 2, 3] as one of the early evidence that mentions about ganita basically, considered as the mathematics which when joining together with jyotisa that is astronomy. Vedanga Jyotisa is placed on the top position in all the sciences same the way crests is situated at the head of peacocks and gems on the heads of snakes is mention in the sloke 1.1. It is considered as one of the oldest text whose actual author is not known, has given the concept of the lunisolar calendar by providing the accurate length of days, month and years according to the motion of the sun, the moon and the planets. Also, provide the rules for relatively calculating the length of day and night. Has provided the actual length of shortest and the longest day, 12 and 18 muhurtas, according to [4] muhurtas is one-third of the whole day.

#### यथा शिखा मयूराणाम् नागानां मणयो यथां ।

Figure 1.1: Sloke mention in Vedanga Jyotisa

Buddhist literature also mentions ganita considered as among early evidence, it states ganita as in three classes namely mudra meaning finger arithmetic, ganana meaning mental arithmetic, samkhyana meaning higher arithmetic in general [5] The scope of hindu ganita is extremely large [2] including the mathematical geometry, and beautifully elaborated in the sthanangasutra mention in the sloke 1.2 in which each word represent the versatility of the hindu mathematics. The sutra comprises of the following words, Parikarma "fundamental operations", vyavahara "determination", Rajju "rope" that means geometry, Rasi "rule of three", Kalasavarna "fractional operations", Yavat tavat "simple equations", Varga "quadratic equations", Ghana "cubic equations", Varga-varga "biquadratic equations, and Vikalpa "permutations and combinations". The word Rajju or sulba is also used in Atharvaveda and Yajurveda is considered as the measuring instrument and used for constructing various mathematical geometry[6].

## परिकम्मम् ववहारो राज्जु रासी कलास्वन्ने यः । जावन्तावति वग्गो घनो ततः वग्गवग्गो विकप्पो तां ।

Figure 1.2: Sloke for Sthanangasutra

In later studies ganita is considered as samkhyana as mention in Buddhist literature and rest is excluded from the scope of mathematics. And the words like pati-ganita and dhuli-karma is used for samkhyana, higher arithmetic. Later the part of ganita dealing with algebra named as bija-ganita, bija-ganita is viewed separately from pati-ganita remain preserved by scholars in coming centuries.

If we talk about the evolution of Hindu numerals than Yajurveda Samhita is one of the early evidence as it mention the list of numerals like Eka (1), dasa (10), sata (100), sahasra (1000), ayuta (10,000), niyuta (100,000), prayuta (1,000,000), arbuda (10,000,000), nyarbuda (100,000,000), samudra (1,000,000,000), Madhya (10,000,000,000), anta (100,000,000,000), parardha (1,000,000,000,000) even the same list is also mentioned in Taittiriya Samhita [7]. There are multiple evidences which show that in early stages numbers are represented in full words but signs are used for smaller numbers. Inscription of Asoka contemplate an evidence to state that the people at that time use script namely Brahmi and Kharosthi. The Brahmi numerals are found in almost all over india during the period of King Asoka (300 BC) and is considered as the pure hindu invention. Brahmi regarded as the mother of Narari numerals which is currently used as hindi numerals for mathematics.

One of the important sutra from the vedic literature which can be considered as the basic concept behind the development of binary computer machine is Pingala chandah-sutra [8]. Which provide the oldest evidence for the use of zero by Pingala (before 200 BC) as mention in the sloke 1.3. In this sutra the solution for finding the total number of arrangements of two things in n places is identified. According to

## द्विरर्धे रूपे शून्यम्। द्विः शून्ये तावदर्धे तद्गुणितम्।

Figure 1.3: Sloke for Pingala Sutra

Pingala chandah-sutra, "write two when the number is halved and write zero when one is subtracted. And in the separate column do double, when zero and square when halved." Let us see an example where n = 7, which is representing the number of places. According to sutra as the value of n is odd that is it can't be absolutely divisible by two so subtract unity that is one form n, write the value of n that is six in column A and write zero for the operation performed in column B. As now the value of n is 6 which is absolutely divisible by two so divide n by two which is represented as halved in the sutra, write the remaining value of n in column A and two for the operation in column B respectively. Now repeat the procedure till the value of n is not equal to zero. Now starting with the last digit in column B which is zero, in this case, we take unity in the last row of column C and double it that will be two. Moving to the second last row, the value of the last row of column C will be either doubled and square according to the value of B in that particular row as shown in Table 1.1. And the process will continue for all the values of column B, after completing the procedure the value of the first row of column C represent the total number of the arrangement of two things in seven places which is  $2^7$  in this case.

Table 1.1: Pingala chandah-sutra

|            | $\mathbf{A}$ | B | $\mathbf{C}$ |

|------------|--------------|---|--------------|

| n = 7      |              |   |              |

| Subtract 1 | 6            | 0 | $2^{7}$      |

| Halved     | 3            | 2 | $2^{6}$      |

| Subtract 1 | 2            | 0 | $2^{3}$      |

| Halved     | 1            | 2 | $2^{2}$      |

| Subtract 1 | 0            | 0 | 2            |

There are several other manuscripts where the evidence of the use of zero has been found such as Bakhshiali Manuscript (200 AD) and Panca-siddhantika (505 AD) where zero is mentioned at several places.

Various scholars from the Vedic period provide various methods of multiplication and also did commentary on various already developed methods. Here some of the methods are highlighted which were mentioned by various scholars named Arayabhata I, Bhaskara I, Brahmagupta, Sridhara, Mahavira, Arayabhata II, Sripati, Narayana, Bhaskara II, Ganesha in their commentary.

#### 1.1.1 Kapata – sandhi

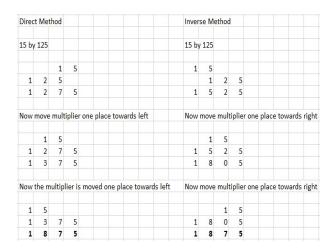

Kapata means "door" and sandhi means "junction" so, the name represents the closing of the door. This is one of the most common methods mentioned by Sridhara, Arayabhata II, Sripati, Mahavira, Bhaskara II, and Narayana. According to Sripati this method state that "Placing the multiplicand below the multiplier as in the junction of two doors multiply successively by moving the multiplier in direct and inverse order" [1] as shown in the Fig. 1.4

Figure 1.4: Kapata - sandhi method

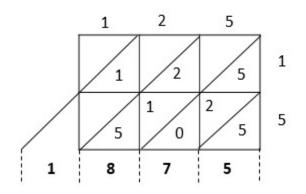

#### 1.1.2 Gelosia method

The method is mention in "Ganita – manjari" also appear in Ganesha commentary on lilavati [9]. In this method, a bigger rectangle/square is divided into multiple small squares depending on the number of digits in the multiplier and multiplicands, and each square is divided diagonally. If each multiplier and multiplicand is of two digits than the square will be divided into four equal parts and each part is separated diagonally. As shown in the example below where the multiplier is 125 and multiplicand is 15 so the square is divided accordingly, then the multiplier is written as the title of each column starting from the leftmost side. And multiplicand is written at the end of each row, and each box is departed diagonally as shown in Fig 1.5. Now the first digit that is 1 of the multiplicand is multiplied with each digit of the multiplier (1, 2, 5) separately and resultant is written in the second half of the corresponding box of the multiplicand and first half of the box will contain generated carry if any. The same procedure is done with another digit of multiplicand that is 5 in this case. Finally, the sum of diagonal digits is carried out to get the final result.

Figure 1.5: Gelosia method

#### 1.1.3 Vajrabhyasa method

The method in [10] mention as a crosswise or zigzag multiplication, many Hindu scholars such as Mahavira, Sridhara, Sripati has referred the method in their work in just simple words. Ganesha has also mentioned the multiplication method and considers it as one of the fantastic methods which require traditional knowledge. In the case of Vajrabhyasa [2] after placing multiplier below multiplicand, multiply unity with the unity of both and store the result, then unity with tens and tens with unity adding them, place the result separately and so on to get the final result. As shown in Fig. 1.6 where the multiplier is 125 and multiplicand in 015, the underbar digits represent the digits to be mention in the final result and the overbar digit represents the carry for the next operation. So, starting from the first operation were the unity of both multiplier and multiplicand are multiplied resulting 25 so 5 will be the last digit of the final answer and 2 will be the carry for a result of the next operation. And with likewise operation final result will be 01875.

Figure 1.6: Vajrabhyasa method

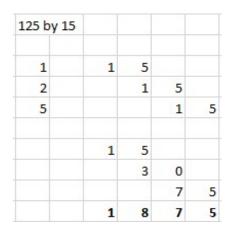

### 1.1.4 Sthana – Khanda

The method has been mention in the work after 628 AD. Bhaskara II defines the method as "Multiply separately by the places of figures and add together"[11]. Numerous scholars made the commentary on the method, an example of the same is shown in the Fig 1.7 where multiplicand 15 is multiplied with each digit of multiplier that is 125 and is added together for the final result that is 1875.

| 125 by | 15 |   | - |   |  |

|--------|----|---|---|---|--|

|        | 1  | 2 | 5 |   |  |

| 1      | 5  |   |   |   |  |

|        | 1  | 5 |   |   |  |

|        |    | 3 | 0 |   |  |

|        |    |   | 7 | 5 |  |

|        | 1  | 8 | 7 | 5 |  |

Figure 1.7: Sthana - Khanda method

#### 1.1.5 Gomutrika method

The method has been described by Brahmagupta, both Sthana – Khanda and Gomutrika methods almost resemble with the way of multiplication of present days. Both methods can be applied for doing multiplication on paper which separates them from the category of pati-ganita. Example is shown in Fig 1.8

Figure 1.8: Gonutrika method

### 1.1.6 Ista – Ganana method

The procedure is noticed in every Hindu work and discussed by many Hindu scholars. The method requires the addition and subtraction of any assumed number. As shown in the example below: 125 by 15 $125 \ge 125(15 + 5) - 125 \ge 5$  $125 \ge 125(15 + 5) - 125 \ge 5$  $125 \ge 125(15 + 5) - 625$  $125 \ge 125 \ge 1875$

Or

$125 \ge 125(15-5) + 125 \ge 5$  $125 \ge 1250 + 625$

$125 \ge 15 = 1875$

Today also multiplication operation is the concern of various researchers for reducing the number of steps required to carry out the multiplication or reducing CPU cycles for the computation of the multiplication operation. As the multiplication and division operation requires more CPU utilization [12], so it always remains an important topic for the researchers to provide the algorithm which requires less utilization of CPU as compared to the current method. Many researchers proposed various algorithm and multiplexer circuit based on mainly two Vedic multiplication method that is urdhva tiryakbhyam and nikhilam sutra [13, 14, 15, 16, 17, 18, 19]. These algorithms and the based multiplexer is totally based on urdhva tiryakbhyam and nikhilam sutra without any modification or any novel approach to reduce the number of CPU cycles for performing the multiplication computation. Inspired from various Vedic multiplication methods discussed above and after learning about the Vedic multiplexer circuits proposed by various researchers, a totally novel algorithm for multiplication is developed and the multiplexer circuit is designed based on the proposed multiplication algorithm. Proposed work is compared with the combinatorial multiplier and Wallace-tree implementation of 8x8 multiplier [20] and it has been found that proposed circuitry is having much lesser gate count and gate delay as compared to the combinatorial and Wallace-tree based multiplier. Furthermore, the proposed work is compared with Vedic multiplexers based on urdhva tiryakbhyam sutra [21] and nikhilam sutra [16], found that the calculated delay of the proposed circuit is much less. The algorithm includes the development of sets and equations, the work is extended for the multiplication of binary numbers for current binary machines. And the circuit of the multiplexer is designed based on the algorithm for the multiplication of two binary numerals.

### 1.2 Ternary(3-state) Logic

Gottfried Leibniz was a German mathematician, after adopting the Indian numerals from 0-9 he convicted that only 0 and 1 are needed to do any mathematical calculations. That means with 0 and 1 all the required mathematical operations can be performed, this calculation was called Binary Number System. He published his work in 1703 AD in an article named Explanation de I' Arithmetic binary. This is how the binary number system came into existence in 1703 AD which is long back before its actual application in digital computers near about 1940's with the invention of transistors moreover we can say with the existence and use of silicon. But the theory of arithmetic remains same as given by Gottfried Leibniz in 1679AD.

So, today's computers are based on the binary number system, which works on two-state (0/1). Basically the logical bit 0 & 1 represents current/no current and in term of voltage it is 0V & 5V [22]. Where 0V is not an absolute 0V but near to 0V and lesser than the threshold voltage of the transistor. From the beginning, the speed of computation or performance of binary machines remains one of the major concerns for numerous researchers. As the speed of computation of the data actually depends on how fast the transition took place that is clock speed, which is at its limit nowadays [23]. In the case of binary machines data is represented and processed in binary form. The binary representation of data requires long strands of 0 and 1 or a large number of bits, which obviously require more processing time and high storage. Moreover, a large number of physical devices are required by the binary computers [24] which results in the overhead of many interconnections [25, 26] and finally bigger chip size & delay. With the concern of some major issues in current binary machines such as performance that is the processing of data (bits), complex circuits, plenty of components, high storage, large number of interconnections, bigger chip, and high delay area results in the introduction to Multi-state Logic. Here, multi-state and multi-valued logic is used interchangeably, we can define multi-state logic as increasing the state of machine from 2-state (binary) to 3-state (ternary) [27] or more states(fuzzy) [28].

Here, the work has been done on ternary logic (radix - 3), ternary logic includes three logical states instead of two that are 0, 1, and 2 to overcome the issues of current binary computer machines. Ternary logic-based computational circuits can enhance the processing speed of data as compared to the machine that works on two states. The number of bits required to represent the data in radix 3 is lesser as compare to the radix 2 so less processing time would be required to process the ternary data. And less storage to store ternary data, which results in higher performance of the ternary logic machine as compare to binary machines. Ternary logic based circuits require less number of electronic components, lesser interconnections overhead and finally smaller chip area [27]. Due to these advantages of ternary over binary logic, ternary logic attracted the interest of many researchers, and many circuits are proposed based on Multivalued Logic (MVL), circuits based on more than 2 logic states. Multiple circuits based on current (i-MVL) and voltages (v-MVL) are proposed for MVL [29, 30, 31, 32]. In the past 20 years, many circuits are proposed based on ternary logic using complementary metal-oxide semiconductor (CMOS) transistors and carbon nanotube FETs. Most of the author working on ternary logic has given the circuit design of ternary inverter circuit and classify it in three different circuits that are simple ternary inverter (STI), positive ternary inverter (PTI) and negative ternary inverter (NTI) [33, 29, 34, 35, 36, 37, 38] using high load resistors, variable resistors or variable voltage threshold of transistors and considered as the building block of any circuit based on ternary logic. Many circuits of ternary adders are also proposed in last few decades using CMOS [33, 38, 39], MOSFETs [37] and CNTFETs [29, 40].

Already proposed ternary circuits by various authors have used three different inverter circuits that is STI, NTI, and PTI for ternary inverter logic which can not be considered as the extension of almost perfect binary logic. Furthermore this logic of three different inverter circuits for ternary logic can never be extended for higher radix like 4 or 5 state logic. So, it is required that circuits design for ternary logic should be logically based on binary or we can say as the extension of binary logic, moreover having scope to be further extended for higher radix. Ternary circuits proposed by various authors as mention above use high load resistors, variable resistors or variable voltage threshold of transistors to design the ternary circuits for dragging out the required results. Which can not be considered as base work for extending the logic to a higher number of states? The use of transistors with the different threshold values and high load resistors results in the increase of complexity and power consumption of the circuit.

So, for contributing to the field of multi-state logic, the truth table and circuits of various operators based on ternary logic are proposed. That will work on three different logic or three different levels of voltages represented by logical values 0, 1, and 2. Proposed circuits can be considered as the extension of the almost perfect binary system and can further be extended to higher radix(more than 3). Truth table and circuit diagram for *t*-NOT gate,*p*-NAND gate, *s*-NAND gate, *p*-NOR gate, *s*-NOR gate, adder, decoder based on ternary logic are proposed, where binary AND and OR gate are considered as MIN and MAX gate for ternary circuits. A novel algorithm for ternary addition based on ternary logic is proposed and which can be applicable for machines with more logical states if developed in the future. Here the term bit is used for representing any one of the logical states among three states (0, 1, and 2) of ternary logic which is the same as in case of binary logic in which either 0 or 1 is considered a bit. The proposed circuits for ternary logic are based on the concept of considering a different range of voltage for representing three different logical states of 0, 1, and 2 as shown in table 1.2.

Table 1.2: Voltage representation of the logical states of ternary logic, where v is voltage

| State Logic | Voltage Range |

|-------------|---------------|

| 0           | 0 < v <= 1    |

| 1           | 1 < v <= 3    |

| 2           | 3 < v <= 5    |

#### 1.3 Motivation

#### 1.3.1 Multiplication Algorithm

Many researchers proposed multiple multiplexer circuits for current binary computer machines based on Vedic multiplication methods, but almost every researcher used only two Vedic methods namely *urdhva triyakbhyam* & *nikhilam* sutra. And the designed binary multiplexers are the exact depiction of these two Vedic sutras with almost no modification and none of the novel algorithms is derived based on Vedic literature in the past few decades. As the Vedic literature is comprised of a various untouched and simpler method of multiplication that motivates the need for a multiplexer with simpler circuit and high efficiency. Thus, a novel multiplication algorithm based on the study of multiple methods mention in Vedic literature is proposed and a binary multiplexer circuit is also designed referring to the algorithm.

#### 1.3.2 Ternary operators & Adder

As the current binary computer machine work on base 2 that is 0 & 1, so the data is represented in a long series of 0s and 1s which consume more processing time and storage. Moreover, binary circuits require a large number of electronic components which causes interconnection overhead and high delay, which collectively cause more power consumption. All these drawbacks of binary machine strengthen the requirement of Multivalued logic-based machine, which actually work on more than two logical states. So, a novel algorithm is proposed for the addition of ternary bits where ternary logic works on three logical states that are  $\{0, 1, 2\}$  instead of two states as in the case of binary. Truth tables of various ternary gates are presented and circuits are designed on the basis of these truth tables. Moreover, a circuit of the adder is designed for performing addition of ternary bits.

The rest of the chapters are organized as follows. In Chapter 2 related work of multiplication operation and multivalued logic is presented. Chapter 3 describes the proposed algorithm for multiplication and the binary multiplexer circuit based on the algorithm. Chapter 4 comprises of proposed circuit diagrams for inverter circuit, NAND & NOR gate based on ternary logic. The circuit for ternary decoder and adder is also designed and a novel ternary addition algorithm is proposed for the addition of ternary bits. Chapter 5 contains the results of the proposed work. And finally, the conclusion and future scope are presented.

# CHAPTER 2 LITERATURE REVIEW

This chapter is broadly categorized into two sections namely *Multiplication Operation* & *Multivalues Logic*. The first section comprises of the detailed study and related work carried out for the development of a novel approach for performing multiplication operation inspired from the Vedic literature and to design a binary multiplexer circuit based on the algorithm. Similarly, another section consists of related work which is studied for the development of various electronic circuits and algorithm for addition based on ternary logic.

#### 2.1 Multiplication Operation

It is very difficult to find the starting point of ganita, but according to various commentaries and translation done for vedas, Vedanga Jyotisa [1, 2, 3] can be consider as as one of the early evidence that mention about ganita. Vedanga, considered as the mathematics with when join together with jyotisa that is astronomy. Then Vedanga Jyotisa is consider on the top position in all the sciences same the way crests is situated at the head of peacocks and gems on the heads of snakes is mention in the sloke. Vedanga Jyotisa is considered as one of the oldest text whose actual author is not know, has given the concept of luni-solar calendar by providing the accurate length of days, month and years according to the motion of the sun, the moon and the planets. Also provide the rules for relatively calculating the length of day and night. Has provide the actual length of shortest and the longest day, 12 and 18 muhurtas, according to [4] muhurtas is consider as one-third of the whole day. Different types of ganita like finger mathematics, mental arithmetic and higher mathematics have also been mentioned in Buddhist literature [2]. The higher mathematics considered as pati-ganita

(procedural mathematics, algorithms) and bija-ganita (mathematics of algebra) both are regarded separately by Sridharacharya [41] in Trisatika (Patiganitasara), Patiganita, Bijaganita, Navasati, and Brhatpati. Similarly, the Yajurveda Samhita [7] is considered as the early source of hindu numerals providing the list of hindu numerals of large numbers. The same list of hindu numerals were seen in taittiriya, maitrayani and kathaka Samhita. Datta et al. [2] discussed about various Vedic method of qu*nana* the common hindu name for multiplication, in various Vedic literature the term gunana, vadh also used for multuplication which actually mean killing or destroying. The author has tried to find out the beginning of muliplication by discussing about various historical literature that mention about the multiplication operation like word abyasa in the work sulba (800 b.c.) used for both addition and multiplication, Aryabhata I (yr. 499), Brahmagupta (yr. 628), Sridhara and many later studies have been used the word *hanana*, *parasparakrtam* used in Bakhshali Manuscript. Define the multiplication as "the process of repetitive addition of multiplicand as many times equal to the multiplicator" mention in Aryabhatiya & Lilavati where the term gunya used for multiplicator and *gunaka* for multiplicand the product of two is termed as *quana-phala*. The author has mention the various Vedic methods discussed by early age mathematicians like gomutrika, khanda, bheda & ista by Brahmagupta, kapatasandhi, tastha, rupa-vibhaga & sthana-vibhaga by Sridhara, Mahavira, Bhaskara II, *gelosia* by Ganesa etc. Various distinct old Hindu methods of multiplication from the pages of Vedic litrature discussed in detail which includes kapata-sandhi, gelosia, tastha, sthana-khanda, gomutrika, istagunana. Sharma et al. [42] discussed about the brahma sphuta siddhanta which mention the various methods of twenty arithmetic operations like addition, subtraction, multiplication, division, square, square-root, cube, cube-root, five standard forms of fractions, the rule of three, etc. The authors have discussed particularly four methods of multiplication gomutrika, khanda, bheda and ista. even the most common and known method kapata-sandhi has not been

discussed by the author in his work. Gomutrika and sthana-khanda method of multiplication are consider to be resemble with each other, khanda method is explained in two different ways by breaking the multiplier into various parts. And it is also mention that is a gunana multiplication method is gone out of india and adopted by Arabs and in Europe. Colebrooke et al. [10] have discussed eight operations in arithmetic methods mentioned in LILAVATI, treatise of Bhaskaracharya. The authors have mentioned multiple examples based on the various method for performing these eight arithmetic operations. According to the author, LILAVATI mention the various method of multiplication which include *rupa-vibhaqa* dividing the multiplicator into parts, sthana-vibhaga considering each digit of multiplicator separately and ganesha in which product goes along the compartments. In [43], the work provided the rules for solving problems involving linear equations, indeterminate equations of the second degree, arithmetical progressions, quadratic equations, approximate evaluations of square roots, complex series, problems of type  $x(1-a_1)(1-a_2)\dots(1-a_n) = P$ , the computation of the fineness of gold, income and expenditure, profit and loss. Various example of multiplication are mentioned including dvigunam, asta gunam, gunita jatam, gunita jata, anena gunitam jatam, phalam. The authors in [44], have discussed the Bija-Ganita of Bhaskara and also presented topics from Brahmagupta's Ganita and Bhaskara's Lilavati. In Arithmetic, various rules for performing fundamental operation, multiplication, division, squaring, square root, cubing, cube root, summation and vyutkalita are explained. Nowadays, many researcher are working on the utilization of various Vedic methods of arithmetic to propose architectures for adders, multiplexers to enhance the performance of the current binary machines. Basically binary machine work on 0 & 1 Leibniz et al. |45| in their work proposed the binary number system that is 0 and 1 and propose the method or performing all the basic mathematical operations such as addition, multiplication, subtraction and division based on binary number system. This theory prove to be the base for the development of binary computer machines after the invention of silicon. Vedic hindu mathematics also shows the evidences of binary number system in Pingala chandahsutra [8], which calculated the total number of arrangements of n things in m places. According to [12], the large percentage of CPU cycle utilization in performing multiplication and division operation. The authors have designed the multiplexer totally based on combinational logic for generating the product of two numbers. The basic idea for enhancing the speed of computation of multiplication process is to either reduce the number of summands or accelerating the process of formation/addition of summands. Thapliyal et al. [13] used the Vedic method named Urdhva Tiryakbhyam and proposed a design of multiplier and square architecture to enhance the speed of computation for performing the multiplication of two numbers and reducing the power consumption. The Vedic method is used for generating partial product in parallel and doing the summation of the partial products. The concept is based on generating the partial product at once and performing concurrent addition of all the partial products, the 4x4 multiplication procedure using Urdhva Tiryakbhyam is shown which can be generalized to nxn bit number, this parallelism reduce the time complexity for the operation. The author has used the Vedic method Urdhva Tiryakbhyam for calculating the square of a number. In [14], the author has design the multiplexer based on Vedic multiplication method called urdhva triyakbhyam to enhance the speed of computation and low the power consumption. Two Vedic methods namely urdhva triyakbhyam & nikhilam sutra has been discussed in detail. The design of multiplexer proposed in the paper based on *urdhva triyakbhyam* multiplication method shows the problem of high propagation delay in case of applying multiplication operation for large numbers. Proposed multiplexer work on the basis of generating all partial products and summing up in a single step. The work is compared with array multiplier on the basis of number of multiplication and addition operations. Dhillon et al. [15] proposed a reduced-bit multiplication algorithm using the *urdhva triyakbhyam*

& nikhilam sutra, both the Vedic multiplication methods are discussed in detail and also mention various other multiplication method from the Vedic literature. Author mentioned that the multiplier design on the basis of *urdhva triyakbhyam* is very much similar to the array multiplier and leads high carry propagation delay in multiplying large numbers, where as the multiplier designed on the basis of *nikhilam sutra* can over come the problem of carry propagation delay. And consider the multiplier based on *nikhilam sutra* as more efficient in performing multiplication among large numbers. In the proposed reduced-bit algorithm author basically use the process of right shift operation with both multiplicand and multiplier to remove the consecutive zeros from the least significant bits. The authors in [46], discussed that is conventional booths algorithm generates an extra partial product bit at least significant position of each row pf partial product that generate irregular array of partial product. This overhead of generating partial product bit caused increase in delay, area and power consumption. The author has proposed a modified booths algorithm which generated a regular shaped partial product array as compared with [47, 48] that reduced the overhead of partial product bit so that area, delay and power consumption also get reduced in modified booths algorithm. Pradhan et al. [16] explain the multiplication methods urdhva triyakbhyam & nikhilam sutra in detail and discussed about the 16x16 multiplexer architecture based on *urdhva triyakbhyam sutra*. The author modify the 16x16 multiplexer based on *urdhva triyakbhyam sutra* using *nikhilam sutra* for reducing the propagation delay. A new high speed architecture has been proposed in [18], for the multiplexer based on the Vedic method of multiplication nikhilam sutra. The proposed architecture of multiplexer is based on the concept of finding the complement (difference) of large operand with its nearest base. The multiplication and addition of the complement of two large operands was performed instead of multiplication of two large operands. The result of the architecture was also compared with the earlier multiplier architecture to show the better utilization and high speed of the binary machine. The author in the paper conclude that the proposed multiplication approach work more efficient when the operands are greater than the half of the base of the operands. James et al. [19] proposed a design of 2-bit multiplexer using Urdhva Thirayakbhyam sutra based on memristive threshold logic, where memristive threshold cell is designed using operational amplifier and CMOS. Where operational amplifier is used as voltage comparator which takes an input voltage and compare it with reference voltage and give the output voltage accordingly. The author concluded that the multiplexer based on Vedic method Urdhva Thirayakbhyam sutra using MTL will be more efficient for the multiplication of large numbers, require low power and reduced the chip area. The author in [49], proposed the multiplier based on Urdhva-Tiryakbhyam method using carry select adder and XOR gate. The basic mathematical calculation of Urdhva-Tiryakbhyam method is discussed in the paper and design of 16x16 multiplier is shown and conclude that the multiplier consume low power and enhance the speed of multiplication. The work is compared with [50] on the basis of latency, in which author has discussed two multiplexer design based in UCLSA (Uniform Carry Select Adder) & VCSLA (Variable Carry Select Adder) and compare both the design. The comparison conducted by author conclude that multiplexer based on UCLSA reduce the power, delay and area as compare to the multiplexer based on VCSLA. In [21], the importance of an algorithm and the feasible hardware for doing faster multiplication and addition in the field of Digital Signal Processing (DSP) has been discussed. The Urdhva tiryakbhyam considered as a fast method of multiplication and discussed in detail and the proposed algorithm is based on calculating the sum of partial product in parllel. The work is compared with the Booth Wallace multiplier on the basis of combinational delay. Also, the authors have mentioned the use of Vedic multiplication methods and their implementation on 8085 and 8086 microcontroller. The author in [51], proposed a design of multiplexer based on Vedic Karatsuba sutra and compared the multiplexer design with the already developed multiplexer based on Vedic *Nikhilam* sutra on the basis of efficiency. Mathematical theory is defined for both the methods in the article, Karatsuba sutra is discussed in detail with example but no such circuit design has been proposed based for multiplexer based on the Vedic method. In [52], multiplication operation is regarded as one of the important operation widely used in various fields like image processing, correlation, signal processing etc [53] so the importance of efficiency of multiplication operation is considered. The author has considered Nikhilam sutra [54] from the pages of of Vedic literature to enhance the performance of multiplication. No such multiplexer circuit is proposed based on the Vedic method, as the mention Vedic method for multiplication is based on addition so the article conclude that the multiplexer design on the basis of Nikhilam sutra would be more efficient then the existing. The author in [55], proposed a multiplication algorithm based on Nikhilam sutra used for binary multiplication. Special case of binary multiplication is carried out using Nikhilam algorithm when both the multiplier and multiplicand are same, on the basis of Nikhilam Squaring algorithm further multiplication is performed. Nikhilam algorithm can be used for the multiplication of number with certain range and for very large numbers Karatsuba algorithm [56] would be more efficient. In [53], multiplication is considered as the key operation that require high performance, to enhance the performance author proposed a multiplier based on the Vedic methods Urdhva and Nikhilam sutras. The mathematical model for both Urdhva and Nikhilam sutras has been explained, objective of the proposed work is to enhance the computation speed of multiplication operation on the basis faster addition [57]. Drawbacks of various multiplexers has been discussed like efficiency of serial multiplexers are lower than that of parallel multiplexer but at the same time parallel multiplexers(Wallace tree multiplier, Booth multiplier, Array multiplier etc) [57, 58] generate higher delay with high power consumption and require large number of logic gates. Summary of related work is shown in Table 2.1, where we noticed that most of the researcher have proposed the design for multiplexer for reducing the processing time of multiplication operation using mainly two Vedic methods, namely, urdhva tiryakbhyam sutra and nikhilam sutra.

| Author & Year                     | Methodology Used                                             | Proposed Work                                                                                                                                   |

|-----------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Dhillon et al. [15],<br>2008      | Urdhva tiryakbhyam and Nikhilam                              | Reduced bit multiplication algorithm<br>and Multiplexer architecture                                                                            |

| Jacobsohn, D [12],<br>1964        | Purely combinational logics,<br>using diode-transistor logic | Design of Multiplier                                                                                                                            |

| Kuang et al. [46],<br>2009        | Enhance the conventional<br>Modify Booth encoding            | Reducing the area, delay and<br>power consumption of conventional<br>Modify Booth encoding                                                      |

| Pradhan et al. [18],<br>2014      | Nikhilam sutra                                               | Design of Multiplexer,<br>for increasing the speed of<br>multiplication operation.                                                              |

| Pradhan at al. [16],<br>2011      | Urdhva tiryakbhyam sutra<br>and nikhilam sutra               | Architecture of 16x16 multiplexer<br>using urdhva tiryakhbyam sutra and<br>extends the existing 16x16 multiplexer<br>based on nikhilam sutra    |

| Pushpangadan at el. [21],<br>2014 | Urdhva tiryakbhyam sutra                                     | Discuss the importance of<br>Vedic approach of multiplication in<br>field of DSP<br>and architecture based on 8085,<br>8086 microcontroller.    |

| Saha et al. [17],<br>2014         | Dhvajanka sutra                                              | Transistor based architecture<br>of division circuit,<br>for reducing the propagation delay<br>and power consumption.                           |

| Thapliyal et al. [13],<br>2004    | Urdhva Tiryakbhyam sutra                                     | Design of multiplexer to<br>reduce the computation time<br>for multiplication operation<br>of two numbers.                                      |

| Tiwari et al. [14],<br>2008       | Urdhva Tiryakbhyam sutra                                     | Discuss various<br>Vedic multiplication methods<br>and their importance.<br>Extended the urdhva tiryakbhyam sutra<br>for binary multiplication. |

Table 2.1: Summary of Related Work

# 2.2 Multivalued Logic

Many researcher propose the concept of MVL to enhance the performance of the binary machine and overcome the flaws of existing binary computers. From the past few decades, researchers have proposed various circuit designs for logic gates based on the concept of ternary logic that is 3 logical states instead of two which can be an alternate for binary logic to enhance the speed of computation [59], to reduce the power consumption, delay and chip area. As the current binary circuitry require large number(plentiful) of electronic components [24], interconnection overhead [25, 26, 32, 60, 61, 37, 62] and large chip area [31, 63]. MVL can be considered as an increasing number of states in the current logic, which can be ternary or fuzzy. Many researchers consider fuzzy [23, 64, 28, 65] logic as infinite numbers of states in

term of MVL, but in case of a mathematical model based machine base, 10 should be considered as a generic machine for computation of all kinds of arithmetic operations. Ternary inverter circuit proposed by many authors and considered as the building block for various other ternary circuits like a ternary adder, decoder, etc [30, 33, 36]. Numerous researchers consider the symmetry of sign conversion [66, 67, 68, 69] to introduce the concept of ternary arithmetic considering -1,0 and +1 as the 3-state logic. Somewhere the ternary bits also represented as N(-1), Z(0), and P(1), Parhami et al. [70] proposed the binary representation of balanced ternary numbers and each ternary digit is represented by at least two binary bits. And consider three states of ternary logic and N, Z, P instead of numeric. It also depicted the truth table for sum and carry of half adder based on 3-state logic using characters(N, Z, P). In initial state ternary logic is considered as an extension of 2-state that is binary logic to treat the ambiguous or uncertain state of a machine. Yamamoto et al. [71] stated that it is not always possible to represent the status of the machine in 2-states that is ON/OFF, the machine can be in the uncertain state also and this ambiguous state is considered as third state logic. This third state is represented by 1/2, the author categorizes ternary logic into two functions that is regular and the majority, where regular ternary logic is considered as a suitable way for treating the ambiguity, means when the state of the machine is not defined. Also mention about the use of B-ternary logic [72] function for the detection of hazards. The  $\leq$  is considered as an ambiguity relation and defined as  $0 \leq 1/2$  and  $1/2 \leq 1$ . In [27], the author also mentions ternary logic suitable for treating the ambiguous state where it is not possible to decide the state of the machine is 0/1 or ON/OFF or TRUE/FALSE. The author has considered the transition state from 0 to 1 or from 1 to 0 as the ambiguous state in which we can't define the state of the machine in either 0 or 1. And another example of an uncertain state is considered as the initial state of any circuit which can be in either of the state between 0 and 1 so, it is considered as an uncertain or ambiguous state by the author which can be treated with ternary logic. The main objective of considering the uncertain or ambiguous state of a circuit is to design a logic circuit with the properties of fault tolerance. And for that binary logic is extended for third uncertain state and it is considered as ternary logic. Allen et [24] have discussed the requirement of MVL over binary logic. Depicted about al. the drawbacks of binary machines which include the requirement of a large number of electronic components for the circuitry and mention that a binary model is not a suitable mathematical model for all integer values. The Boolean algebra based on the binary logic cant be used or extended for other higher base mathematical models so, the computers based on binary logic cant be considered as the perfect machine. Also mention about the concept of multivalued logic [73, 74, 75, 76] where the realization of the ternary switching circuit is proposed on the basis of diodes and transistors. And propose a switching theory based on the concept of ternary logic. Smith et al. [31] mention the problem of interconnections in the current binary machine which grows exponentially high with an increase in the number of components that grow the chip area. And stated the solution as the introduction to MVL for reducing the interconnection overhead in case of binary circuits. The author has provided the notations for MVL taking an example for base 4 circuits considering four logical states that are 0, 1, 2, 3 and stated that the state varies in a circular manner. This means that every state in mention set 1, 2, 3, 0 is always one logic higher than state 0, 1, 2, 3. In [32], the author discusses the unacceptability of the binary logic as it doesn't fit with the mathematical decimal model which makes the requirement of MVL. The current binary machine works on the strings on 0's and 1's it is only because of the invention of diode based on silicon which works as a switch ON/OFF which is not according to the mathematical model based on decimal numerals. The author stated that machines based on higher radix exponentially reduce the wiring complexity and reduction in ternary logic gates. Also mention about the types of circuits for MVL