Name: **Enrolment No: UNIVERSITY OF PETROLEUM AND ENERGY STUDIES End Semester Examination, May 2019 Programme Name: B.Tech Electronics Engineering** : VIII Semester Course Name : VHDL Time : 03 hrs : ELEG 434 **Course Code** Max. Marks: 100 Nos. of page(s) : 02 Instructions: Assume any data in programming, if required **SECTION A** (5  $\times$  4 = 20 Marks) S. No. Attempt *all* the questions Marks CO What is entity and architecture is VHDL programming. Explain with examples. **Q1** 5 **CO1** Q.2 What is the concept of package in VHDL programming. Explain with example. 5 **CO2** 0.3 Write the VHDL code for the positive edge triggered asynchronous T flip flop. Detail the 5 **CO4** functionality of the chip. Compare CPLD, FPGA and ASIC based on their structure. Q.4 5 **CO5 SECTION B** (4 x 10 = 40 Marks) Attempt *all* the questions Q.5 What modeling styles are followed in VHDL based design. Design the chip of 2 x 4 decoder in all 10 CO<sub>2</sub> style of modeling. Draw the logic diagram for the same. Q.6 Design the 4-bit priority encoder or checker using VHDL. Detail the functionality of the chip with 10 CO3 truth table and logic diagram. **Q.7** How behavioral model is different from data flow model. Design a (16 x 1) multiplexer chip using 10 **CO2** behavioral modeling. 0.8 Detail the synthesis process on FPGA. Explain the FPGA design flow with example. 10 **CO5 SECTION-C** (2 x 20 = 40 Marks) Attempt any *two* of the followings 0.8 The purpose of a Digital Comparator is to compare a set of variables or unknown numbers, for example A (A1, A2, A3, ..., An, etc) against that of a constant or unknown value such as B (B1, B2, B3, .... Bn, etc) and produce an output condition or flag depending upon the result of the comparison. For example, a magnitude comparator of two 1-bits, (A and B) inputs would produce the following three output conditions when compared to each other. This is useful if we want to compare two variables and want to produce an output when any of the above three conditions are achieved. For example, produce an output from a counter when a certain count number is reached. Consider the case of 64-bit comparator for the different logic functions. ▶ A = B 20 **CO3** ▶ A < B</p> А Magnitude ▶ A > B Comparator A ≠ B в → A ≤ B A≥B

Fig.1

Name:

**Enrolment No:**

## **UPES**

## UNIVERSITY OF PETROLEUM AND ENERGY STUDIES

## End Semester Examination, May 2019

**Programme Name: B.Tech Electronics Engineering**

Course Name : VHDL

Course Code : ELEG 434

Nos. of page(s) : 02

Instructions: Assume any data in programming, if required

| <b>SECTION A (5 x 4 = 20 Marks)</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |     |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

| S. No.                              | Attempt <i>all</i> the questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Marks | CO  |

| Q 1                                 | What is the difference between Mealy and Moore FSM. Explain with example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5     | CO1 |

| Q.2                                 | What is the concept of package in VHDL programming. Explain with example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5     | CO2 |

| Q.3                                 | Write the VHDL code for the positive edge triggered asynchronous D flip flop. Detail the functionality of the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5     | CO3 |

| Q.4                                 | Detail the synthesis process on FPGA. Explain the FPGA design flow with example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5     | CO5 |

|                                     | <b>SECTION B</b> (4 x 10 = 40 Marks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |     |

|                                     | Attempt <i>all</i> the questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |     |

| Q.5                                 | What modeling styles are followed in VHDL based design. Design the chip of $3 \ge 8$ decoder in all style of modeling. Draw the logic diagram for the same.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10    | CO2 |

| Q.6                                 | Design the 4-bit priority encoder or checker using VHDL. Detail the functionality of the chip with truth table and logic diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10    | CO3 |

| Q.7                                 | How structural model is different from data flow model. Design a $(8 \times 1)$ multiplexer chip using behavioral modeling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10    | CO2 |

| Q.8                                 | Realize a full adder using half adders and write VHDL code in structural level modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10    | CO4 |

|                                     | SECTION-C (2 x 20 = 40 Marks)<br>Attempt any <i>two</i> of the followings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |     |

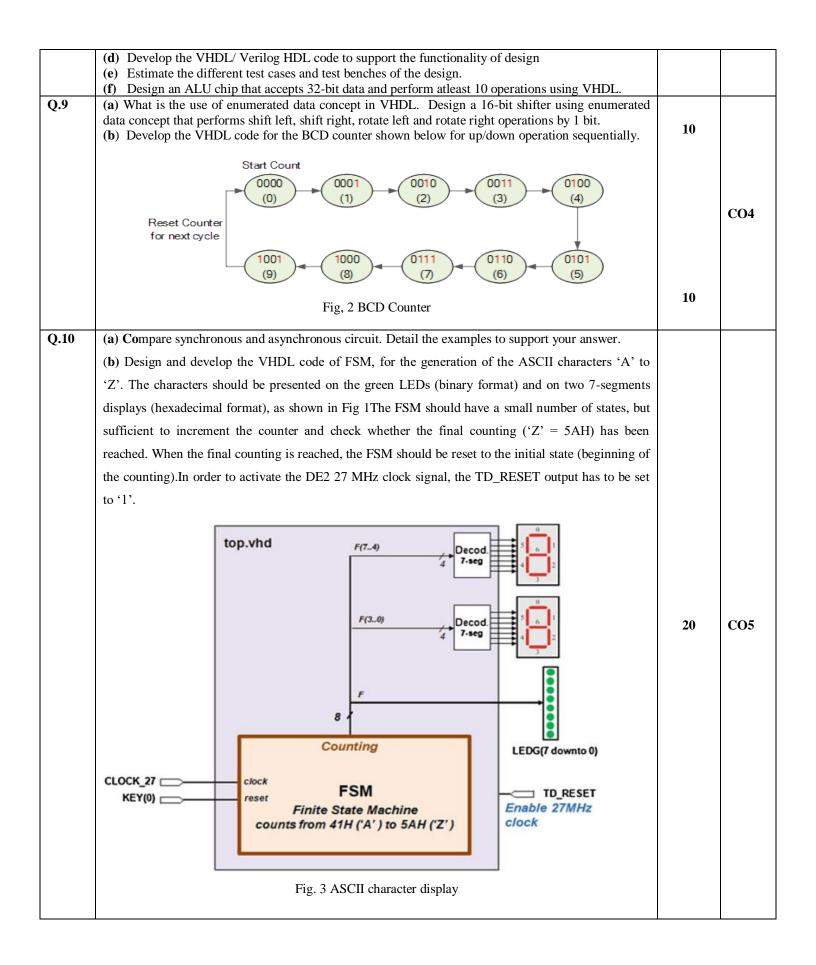

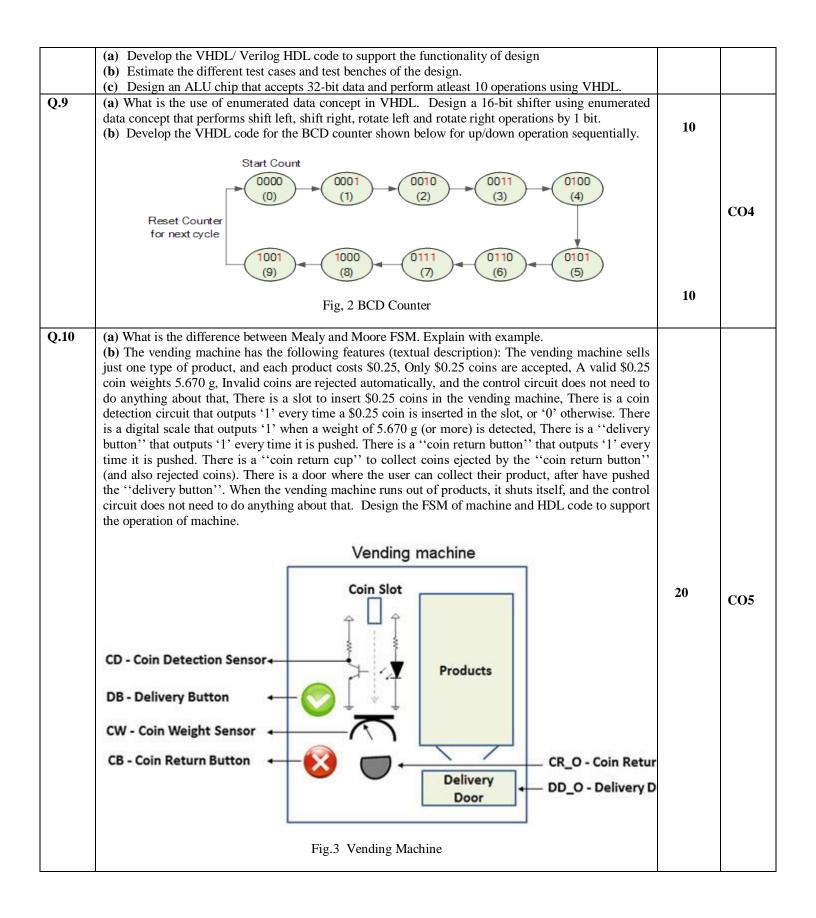

| Q.8                                 | The purpose of a Digital Comparator is to compare a set of variables or unknown numbers, for<br>example A (A1, A2, A3,, An, etc) against that of a constant or unknown value such as B (B1, B2,<br>B3,, Bn, etc) and produce an output condition or flag depending upon the result of the comparison.<br>For example, a magnitude comparator of two 1-bits, (A and B) inputs would produce the following<br>three output conditions when compared to each other. This is useful if we want to compare two<br>variables and want to produce an output when any of the above three conditions are achieved. For<br>example, produce an output from a counter when a certain count number is reached. Consider the case<br>of 64-bit comparator for the different logic functions.<br>A = B<br>A Magnitude<br>Comparator<br>B A $\leq B$<br>B A $\leq B$<br>Fig.1 | 20    | CO3 |

Semester : VIII Time : 03 hrs Max. Marks : 100

FRGY STUDIE